imec:最先端半導体研究を公開!

recherche semi-conducteurs ouverte au public !

Halbleiterforschung für Öffentlichkeit zugänglich!

Semiconductor research open to the public!

半導體研究向公眾開放!

ーIEDM(International Electron Devices Meeting)で発表ー

ーRapidusがimecと共同開発ー

Rapidus:

2022年12月6日、ベルギーのimecと協力覚書に署名した。

MOCに基づき、2nm世代以降の半導体量産を目指す。

協力覚書の概要:

経済産業省Webサイト(12月6日付け)で閲覧できる。

MOCの概要は、いくつかの点で興味深い。

- 要素技術の共同研究は当然のこと。

- EUVの露光技術を名指ししていること。

- ラピダスの技術者をimecに派遣できること。

- 研究開発ロードマップを共同で策定する。

- imecは日本に研究開発チームを設立する。

imecの試作ライン:

ー規模の大きさを象徴する存在ー

「最新製造装置やを並べた、直径300mmウェハ対応の試作ライン」だ。

研究機関が、直径300mmウェハ対応の半導体製造ラインを所有することはない。

IEDM:

ー半導体デバイス技術とプロセス技術で世界最大の国際学会ー

IEDMが、12月5日~7日サンフランシスコで開催された。

imecが、21件と多くの研究開発活動を披露した。

Intelの研究成果発表:

IntelのIEDMにおける発表件数が11件(招待3件、一般8件)で、

「imecの発表件数は、Intelの2倍」である。

imecの最新研究分野:

ーimecがIEDM 2022で公表した研究分野ー

- 「不揮発性メモリ」

- 「CMOSロジックとトランジスタ、配線」

- 「信頼性」

- 「化合物半導体」

- 「センシング」

- 「極低温CMOS回路」

- 「次世代プロセス」と幅広い。

強誘電体メモリ(FeRAM):

ランタンドープの二酸化ハフニウム・ジルコニウム(La : HZO)強誘電体膜で、高性能強誘電体キャパシタを試作(講演番号6.4)

酸化チタン(TiO2)のシード層と酸化ニオブ(Nb2O5)のキャップ層による界面制御が、強誘電体膜の品質向上に寄与。

10の11乗の分極反転サイクルを経ても、残留分極(2Pr)が30μC/平方cmと大きい。

磁気メモリ(MRAM):

外部磁界を必要とせず読み書き出来るスピン軌道トルク方式磁気メモリ(SOT-MRAM)を試作(講演番号36.2)

- CMOSロジックへの埋め込みが可能である。

- 試作メモリセルのスイッチング時間は0.3nsと短い。

- 書き換えサイクル寿命(推定値)は10の12乗を超える。

クロスポイント用セレクタ:

しきい電圧変動メカニズム(講演番号5.1)、有毒物質を除外したセレクタ材料(講演番号8.6)に関する研究成果を発表した。

ーキオクシア派遣の研究者が講演ー

これら2件の発表はいずれも、キオクシアからimecに派遣された研究者が筆頭著者(すなわち講演者)となっている。

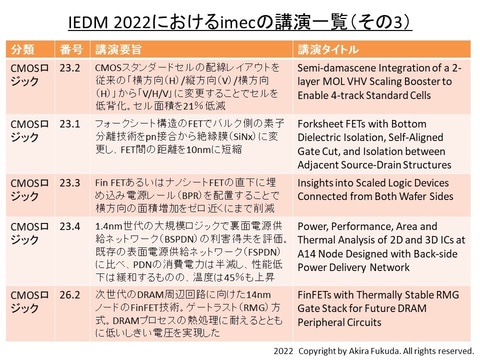

CMOSロジックとトランジスタ、配線:

CMOSロジックとトランジスタ、配線では、加工寸法の縮小に頼らずに、回路面積を小さくする技術や回路寸法を短くする技術が披露された。

いずれも2nm以降の技術ノードに向けた研究成果だ。

CMOSロジック基本回路:

スタンダードセル:

CMOSロジックの基本回路となるスタンダードセルでは、多層配線構造を工夫しセルの高さを低くする技術を発表。(講演番号23.2)

- スタンダードセル面積を従来より21%削減。

- セルの高さを5トラックから4トラックへ低くし、面積縮小に寄与した。

フォークシート構造:

FETの距離を短縮:

フォークシート構造(ナノシート構造の改良版)で、隣接するFET距離を10nmと短くする技術(講演番号23.1)

埋め込み電源供給配線(BPR)をトランジスタの直下に配置し、シリコン面積の増加をゼロにする技術(講演番号23.3)

ウェハ裏面側の電源供給ネットワーク(BSPDN)の課題が、放熱であることを指摘した報告(講演番号23.4)

半導体デバイスの研究開発:

「信頼性」は非常に重要な位置を占める。

トランジスタの長期信頼性(寿命)を制約する不良メカニズムは主に2つ。

- 1つはバイアス温度不安定性(BTI)、

- もう1つは経時的絶縁破壊(TDDB)である。

前者:

長期間の電圧印加によってしきい電圧の変動や相互コンダクタンスの低下を引き起こす。

後者:

長期間の電圧印加によってゲート絶縁膜に絶縁劣化が起こり、絶縁破壊へと至る。

imecのBTI研究成果:

imecはバイアス温度不安定性(BTI)に関する研究成果を2件、IEDM 2022で発表した。

1件目:

次世代のシリコンHKMG CMOSでBTIを改善する手法の成果(講演番号30.4)

nチャンネルMOS FETのPBTI:

300℃以下の酸素処理で、

pチャンネルMOS FETのNBTIは、300℃以下の水素処理で改善することを示した。

2件目:

IGZO(インジウム・ガリウム・亜鉛の酸化物)チャンネルTFT(薄膜トランジスタ)のBTI劣化測定手法に関する発表(講演番号30.1)

波長の異なる光を照射しながら、電流電圧特性を測定することで、BTI劣化特性を把握し、精度の高い劣化モデルを構築した。

このほか信頼性関連:

極低温環境でCMOSが発生する過剰f分の1雑音の原因推定(講演番号30.5)、

GaN HEMTのバックバリアによるオン抵抗分散(講演番号30.6)、

GaN HEMT(Si基板上)の静電気放電(ESD)耐性(講演番号30.7)研究成果を発表した。

「化合物半導体」、「センシング」、「極低温CMOS回路」、「次世代プロセス」

合計で6件の講演があった。

化合物半導体とセンシングが2件、そのほかは1件ずつである。

ラピダスが今後、どのような研究テーマにエンジニアを派遣するのか。

その選択が興味深い。

【福田昭のセミコン業界最前線】

– PC Watch

https://pc.watch.impress.co.jp/docs/column/semicon/1466624.html

imec : la recherche de pointe sur les semi-conducteurs ouverte au public !

ーAnnoncé à l’IEDM (International Electron Devices Meeting)ー

ーRapidus développé conjointement avec l’imecー

Rapide :

Le 6 décembre 2022, un protocole de coopération a été signé avec l’imec de Belgique.

Basé sur MOC, nous visons à produire en masse des semi-conducteurs après la génération 2nm.

Aperçu du protocole de coopération :

Il est consultable sur le site du ministère de l’Economie, du Commerce et de l’Industrie (en date du 6 décembre).

La vue d’ensemble du MOC est intéressante à plusieurs égards.

La recherche conjointe sur les technologies élémentaires va de soi.

Il fait référence à la technologie d’exposition EUV.

Possibilité d’envoyer des ingénieurs de Rapidus à imec.

Élaborer conjointement une feuille de route R&D.

imec établira une équipe de recherche et développement au Japon.

La ligne de prototypes d’Imec :

ーExistence qui symbolise la taille de l’échelleー

Il s’agit d’une « ligne prototype pour wafers de 300 mm de diamètre, équipée des derniers équipements de fabrication ».

Un institut de recherche ne possède pas de chaîne de fabrication de semi-conducteurs capable de traiter des tranches de 300 mm de diamètre.

IEDM :

ーLa plus grande conférence internationale au monde sur la technologie des dispositifs semi-conducteurs et la technologie des procédésー

L’IEDM s’est tenu à San Francisco du 5 au 7 décembre.

l’imec a dévoilé 21 activités de recherche et développement.

Annonce des résultats de recherche d’Intel :

Le nombre de présentations à l’IEDM d’Intel était de 11 (3 invités, 8 généraux),

“Le nombre d’annonces imec est le double de celui d’Intel.”

Les derniers axes de recherche d’Imec :

ーDomaines de recherche annoncés par l’imec à l’IEDM 2022ー

“Une mémoire non volatile”

“Logique CMOS, transistors et câblage”

“fiabilité”

« Semi-conducteur composé »

“Sentir”

“Circuit cryogénique CMOS”

Une large gamme de “procédés de nouvelle génération”.

Mémoire ferroélectrique (FeRAM):

Condensateur ferroélectrique prototype à haute performance avec film ferroélectrique de dioxyde d’hafnium-zirconium dopé au lanthane (La: HZO) (Conférence n ° 6.4)

Le contrôle de l’interface par une couche germe d’oxyde de titane (TiO2) et une couche coiffe d’oxyde de niobium (Nb2O5) contribue à améliorer la qualité des films ferroélectriques.

Même après 10 11 cycles d’inversion de polarisation, la polarisation rémanente (2Pr) atteint 30 μC/cm 2 .

Mémoire magnétique (MRAM):

Mémoire magnétique prototype de type couple spin-orbite (SOT-MRAM) pouvant être lue et écrite sans champ magnétique externe (Conférence n ° 36.2)

L’intégration dans la logique CMOS est possible.

La cellule mémoire prototype a un temps de commutation court de 0,3ns.

La durée de vie du cycle de réécriture (estimation) dépasse 10 puissance 12.

Sélecteur pour point de croisement :

Nous avons présenté des résultats de recherche sur le mécanisme de variation de tension de seuil (Conférence n° 5.1) et les matériaux sélecteurs excluant les substances toxiques (Conférence n° 8.6).

-Conférence par un chercheur détaché de KIOXIA-

Dans ces deux présentations, les chercheurs détachés de KIOXIA à l’imec sont les auteurs principaux (c’est-à-dire les conférenciers).

Logique CMOS et transistors, câblage :

Pour la logique CMOS, les transistors et le câblage, des technologies permettant de réduire la surface du circuit et de raccourcir les dimensions du circuit sans compter sur la réduction de la taille du processus ont été présentées.

Tous sont des résultats de recherche pour le nœud technologique après 2 nm.

Circuit de base logique CMOS :

Cellule standard :

Pour la cellule standard, qui est le circuit de base de la logique CMOS, nous avons annoncé une technologie permettant de réduire la hauteur de la cellule en concevant une structure de câblage multicouche. (Conférence numéro 23.2)

La surface de cellule standard a été réduite de 21 % par rapport aux modèles conventionnels.

La hauteur de la cellule a été abaissée de 5 pistes à 4 pistes, contribuant à la réduction de la surface.

Construction du siège de fourche :

Réduisez la distance FET :

Technologie pour raccourcir la distance entre les FET adjacents à 10 nm avec une structure de feuille fourchue (une version améliorée de la structure de nanofeuille) (Conférence n° 23.1)

Une technologie qui élimine l’augmentation de la surface de silicium en plaçant le câblage d’alimentation intégré (BPR) directement sous le transistor (Conférence n ° 23.3)

Un rapport soulignant que la dissipation thermique est un problème du réseau d’alimentation (BSPDN) à l’arrière de la plaquette (Conférence n ° 23.4)

Recherche et développement de dispositifs semi-conducteurs :

La “fiabilité” occupe une place très importante.

Il existe principalement deux mécanismes de défaillance qui limitent la fiabilité à long terme (durée de vie) des transistors.

L’un est l’instabilité de la température de polarisation (BTI),

Un autre est le claquage diélectrique dépendant du temps (TDDB).

ancien:

L’application de tension à long terme provoque une fluctuation de la tension de seuil et une réduction mutuelle de la conductance.

le dernier:

L’application de tension à long terme provoque une détérioration de l’isolation dans le film d’isolation de grille, entraînant une panne diélectrique.

Résultats de la recherche BTI d’Imec :

imec a présenté deux résultats de recherche sur l’instabilité de température de biais (BTI) à l’IEDM 2022.

1er :

Résultat de la méthode d’amélioration du BTI dans le silicium HKMG CMOS de nouvelle génération (Conférence n° 30.4)

PBTI pour les MOS FET à canal n :

Avec un traitement à l’oxygène inférieur à 300℃,

Il a été démontré que le NBTI du MOS FET à canal p est amélioré par un traitement à l’hydrogène en dessous de 300℃.

2ème :

Présentation sur la méthode de mesure de la dégradation du BTI pour le canal IGZO (oxyde d’indium-gallium-zinc) TFT (transistor à couches minces) (Conférence n° 30.1)

En mesurant les caractéristiques courant-tension tout en irradiant la lumière avec différentes longueurs d’onde, nous avons saisi les caractéristiques de détérioration BTI et construit un modèle de détérioration très précis.

Autres liés à la fiabilité :

Estimation de la cause du bruit 1/f excessif généré par CMOS dans les environnements cryogéniques (Cours n° 30.5),

Répartition de la résistance à l’état passant par barrière arrière de GaN HEMT (Conférence n° 30.6),

Un résultat de recherche sur la résistance aux décharges électrostatiques (ESD) du GaN HEMT (sur substrat Si) (Conférence n° 30.7) a été présenté.

” Semi-conducteur composé “, ” Détection “, ” Circuit cryogénique CMOS “, ” Processus de nouvelle génération “

Il y avait un total de 6 présentations.

Deux sont pour les semi-conducteurs composés et un pour la détection, et un pour les autres.

Dans quel type de thème de recherche Rapidus détachera-t-il ses ingénieurs à l’avenir ?

Le choix est intéressant.

[Ligne de front d’Akira Fukuda dans l’industrie des semi-conducteurs]

-Montre PC

imec: Modernste Halbleiterforschung für die Öffentlichkeit zugänglich!

ーAnkündigung auf dem IEDM (International Electron Devices Meeting)ー

ーRapidus gemeinsam mit imec entwickeltー

Rapidus:

Am 6. Dezember 2022 wurde eine Kooperationsvereinbarung mit dem belgischen imec unterzeichnet.

Basierend auf MOC streben wir die Massenproduktion von Halbleitern nach der 2-nm-Generation an.

Übersicht über das Memorandum of Cooperation:

Es kann auf der Website des Ministeriums für Wirtschaft, Handel und Industrie eingesehen werden (vom 6. Dezember).

Die MOC-Übersicht ist in mehrfacher Hinsicht interessant.

Gemeinsame Forschung zu elementaren Technologien ist dabei selbstverständlich.

Es bezieht sich auf die EUV-Belichtungstechnologie.

Fähigkeit, Ingenieure von Rapidus zu imec zu schicken.

Formulieren Sie gemeinsam eine F&E-Roadmap.

imec wird ein Forschungs- und Entwicklungsteam in Japan aufbauen.

Prototypenlinie von Imec:

ーExistenz, die die Größe des Maßstabs symbolisiertー

Es handele sich um eine „Prototypenlinie für Wafer mit einem Durchmesser von 300 mm, ausgestattet mit modernster Fertigungstechnik“.

Ein Forschungsinstitut besitzt keine Halbleiterfertigungsstraße, die Wafer mit 300 mm Durchmesser handhaben kann.

IEDMs:

ーDie weltweit größte internationale Konferenz für Halbleitergerätetechnologie und Prozesstechnologieー

IEDM fand vom 5. bis 7. Dezember in San Francisco statt.

imec stellte 21 Forschungs- und Entwicklungsaktivitäten vor.

Ankündigung von Intel-Forschungsergebnissen:

Die Anzahl der Präsentationen bei Intels IEDM betrug 11 (3 eingeladene, 8 allgemeine),

“Die Zahl der imec-Ankündigungen ist doppelt so hoch wie die von Intel.”

Neueste Forschungsgebiete von Imec:

ーForschungsbereiche, die von imec auf der IEDM 2022 angekündigt wurdenー

“Nichtflüchtiger Speicher”

“CMOS-Logik, Transistoren und Verdrahtung”

“Verlässlichkeit”

“Verbindungshalbleiter”

“Sensing”

“Kryogene CMOS-Schaltung”

Ein breites Spektrum an „Prozessen der nächsten Generation“.

Ferroelektrischer Speicher (FeRAM):

Prototyp eines ferroelektrischen Hochleistungskondensators mit Lanthan-dotiertem Hafnium-Zirkoniumdioxid (La:HZO) ferroelektrischem Film (Vortrag Nr. 6.4)

Die Grenzflächenkontrolle durch eine Keimschicht aus Titanoxid (TiO2) und eine Deckschicht aus Nioboxid (Nb2O5) trägt zur Verbesserung der Qualität ferroelektrischer Filme bei.

Selbst nach 10 11 Zyklen der Polarisationsumkehr ist die remanente Polarisation (2Pr) so groß wie 30 &mgr;C/cm 2 .

Magnetspeicher (MRAM):

Prototyp eines Magnetspeichers vom Spin-Orbit-Torque-Typ (SOT-MRAM), der ohne externes Magnetfeld gelesen und beschrieben werden kann (Vortrag Nr. 36.2)

Eine Einbettung in CMOS-Logik ist möglich.

Die Prototyp-Speicherzelle hat eine kurze Schaltzeit von 0,3 ns.

Die Wiederschreibzykluslebensdauer (Schätzung) übersteigt 10 hoch 12. Potenz.

Selektor für Koppelpunkt:

Wir präsentierten Forschungsergebnisse zum Mechanismus der Schwellenspannungsvariation (Vortrag Nr. 5.1) und Selektormaterialien ohne toxische Substanzen (Vortrag Nr. 8.6).

-Vortrag eines von KIOXIA entsandten Forschers-

Bei diesen beiden Präsentationen sind von KIOXIA an das imec entsandte Forscher die Hauptautoren (dh Referenten).

CMOS-Logik und Transistoren, Beschaltung:

Für CMOS-Logik, -Transistoren und -Verdrahtung wurden Technologien zum Reduzieren der Schaltungsfläche und zum Verkürzen der Schaltungsabmessungen vorgestellt, ohne sich auf eine Reduzierung der Prozessgröße zu verlassen.

Allesamt Forschungsergebnisse für den Technologieknoten nach 2nm.

CMOS-Logik-Grundschaltung:

Standardzelle:

Für die Standardzelle, die die Grundschaltung der CMOS-Logik darstellt, haben wir eine Technologie angekündigt, um die Höhe der Zelle durch die Entwicklung einer mehrschichtigen Verdrahtungsstruktur zu reduzieren. (Vortragsnummer 23.2)

Die Standardzellenfläche wurde im Vergleich zu herkömmlichen Modellen um 21 % reduziert.

Die Zellenhöhe wurde von 5 Gleisen auf 4 Gleise abgesenkt, was zur Flächenreduzierung beitrug.

Gabelsitzkonstruktion:

FET-Abstand verringern:

Technologie zur Verkürzung des Abstands zwischen benachbarten FETs auf 10 nm mit einer gegabelten Blattstruktur (einer verbesserten Version der Nanoblattstruktur) (Vortrag Nr. 23.1)

Eine Technologie, die die Vergrößerung der Siliziumfläche eliminiert, indem eingebettete Stromversorgungsverdrahtung (BPR) direkt unter dem Transistor platziert wird (Vortrag Nr. 23.3)

Ein Bericht, der darauf hinweist, dass die Wärmeableitung ein Problem des Stromversorgungsnetzes (BSPDN) auf der Rückseite des Wafers ist (Vortrag Nr. 23.4)

Forschung und Entwicklung von Halbleiterbauelementen:

„Zuverlässigkeit“ nimmt eine sehr wichtige Stellung ein.

Es gibt hauptsächlich zwei Ausfallmechanismen, die die langfristige Zuverlässigkeit (Lebensdauer) von Transistoren begrenzen.

Einer ist Bias Temperature Instability (BTI),

Ein weiterer ist der zeitabhängige dielektrische Durchbruch (TDDB).

ehemalige:

Langfristiges Anlegen einer Spannung verursacht Schwankungen der Schwellenspannung und eine Verringerung der gegenseitigen Konduktanz.

letzteres:

Das Anlegen einer Langzeitspannung verursacht eine Isolationsverschlechterung im Gate-Isolationsfilm, was zu einem Durchschlag des Dielektrikums führt.

BTI-Forschungsergebnisse von Imec:

imec präsentierte auf der IEDM 2022 zwei Forschungsergebnisse zur Bias-Temperaturinstabilität (BTI).

1:

Ergebnis der Methode zur Verbesserung von BTI in Silizium-HKMG-CMOS der nächsten Generation (Vortrag Nr. 30.4)

PBTI für n-Kanal-MOSFETs:

Mit Sauerstoffbehandlung unter 300℃,

Es wurde gezeigt, dass der NBTI von p-Kanal-MOS-FETs durch eine Wasserstoffbehandlung unter 300 ° C verbessert wird.

2.:

Präsentation zum BTI-Degradationsmessverfahren für IGZO (Indium-Gallium-Zink-Oxid)-Kanal-TFT (Dünnschichttransistor) (Vortrag Nr. 30.1)

Durch Messen der Strom-Spannungs-Charakteristika bei Einstrahlung von Licht mit unterschiedlichen Wellenlängen haben wir die BTI-Verschlechterungscharakteristika erfasst und ein hochgenaues Verschlechterungsmodell konstruiert.

Andere Zuverlässigkeit bezogen:

Abschätzung der Ursache für übermäßiges 1/f-Rauschen, das von CMOS in kryogenen Umgebungen erzeugt wird (Vortrag Nr. 30.5),

On-Resistance Distribution by Back Barrier of GaN HEMT (Vortrag Nr. 30.6),

Ein Forschungsergebnis zur Beständigkeit von GaN-HEMT (auf Si-Substrat) gegen elektrostatische Entladung (ESD) (Vortrag Nr. 30.7) wurde vorgestellt.

“Verbindungshalbleiter”, “Sensorik”, “Kryogene CMOS-Schaltung”, “Prozess der nächsten Generation”

Es gab insgesamt 6 Präsentationen.

Zwei sind für Verbindungshalbleiter und einer für die Sensorik und einer für andere.

Zu welcher Art von Forschungsthema wird Rapidus in Zukunft Ingenieure entsenden?

Die Wahl ist interessant.

[Akira Fukudas Frontlinie in der Halbleiterindustrie]

-PC-Uhr