imec: State-of-the-art semiconductor research open to the public!

ーAnnounced at IEDM (International Electron Devices Meeting)ー

ーRapidus jointly developed with imecー

Rapidus:

On December 6, 2022, a memorandum of cooperation was signed with imec of Belgium.

Based on MOC, we aim to mass-produce semiconductors after the 2nm generation.

Overview of the memorandum of cooperation:

It can be viewed on the Ministry of Economy, Trade and Industry website (dated December 6).

The MOC overview is interesting in several respects.

Joint research on elemental technologies is a matter of course.

It refers to EUV exposure technology.

Ability to dispatch engineers from Rapidus to imec.

Jointly formulate an R&D roadmap.

imec will establish a research and development team in Japan.

Imec’s prototype line:

ーExistence that symbolizes the size of scaleー

It is a “prototype line for wafers with a diameter of 300 mm, equipped with the latest manufacturing equipment.”

A research institute does not own a semiconductor manufacturing line capable of handling 300mm diameter wafers.

IEDMs:

ーThe World’s Largest International Conference on Semiconductor Device Technology and Process Technologyー

IEDM was held in San Francisco from December 5th to 7th.

imec unveiled 21 research and development activities.

Intel research results announcement:

The number of presentations at Intel’s IEDM was 11 (3 invited, 8 general),

“The number of imec announcements is twice that of Intel.”

Imec’s latest research areas:

ーResearch areas announced by imec at IEDM 2022ー

“Non-Volatile Memory”

“CMOS logic, transistors and wiring”

“reliability”

“Compound semiconductor”

“Sensing”

“Cryogenic CMOS circuit”

A wide range of “next-generation processes”.

Ferroelectric memory (FeRAM):

Prototype high-performance ferroelectric capacitor with lanthanum-doped hafnium-zirconium dioxide (La:HZO) ferroelectric film (Lecture No. 6.4)

Interface control by a seed layer of titanium oxide (TiO2) and a cap layer of niobium oxide (Nb2O5) contributes to improving the quality of ferroelectric films.

Even after 10 11 cycles of polarization reversal, the remanent polarization (2Pr) is as large as 30 μC/cm 2 .

Magnetic memory (MRAM):

Prototype spin-orbit torque type magnetic memory (SOT-MRAM) that can be read and written without an external magnetic field (Lecture No. 36.2)

Embedding in CMOS logic is possible.

The prototype memory cell has a short switching time of 0.3ns.

The rewrite cycle life (estimate) exceeds 10 to the 12th power.

Selector for crosspoint:

We presented research results on the threshold voltage variation mechanism (Lecture No. 5.1) and selector materials excluding toxic substances (Lecture No. 8.6).

-Lecture by a researcher dispatched from KIOXIA-

In both of these two presentations, researchers dispatched from KIOXIA to imec are the lead authors (that is, speakers).

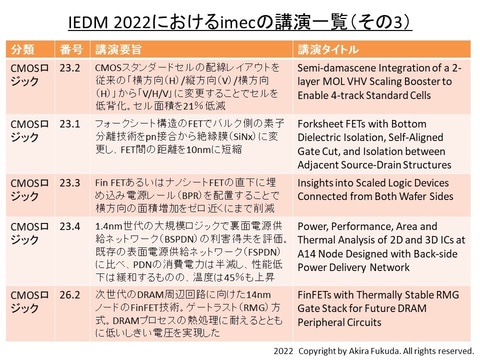

CMOS logic and transistors, wiring:

For CMOS logic, transistors, and wiring, technologies for reducing circuit area and shortening circuit dimensions without relying on process size reduction were presented.

All of them are research results for the technology node after 2nm.

CMOS logic basic circuit:

Standard cell:

For the standard cell, which is the basic circuit of CMOS logic, we announced a technology to reduce the height of the cell by devising a multilayer wiring structure. (Lecture number 23.2)

The standard cell area has been reduced by 21% compared to conventional models.

The cell height was lowered from 5 tracks to 4 tracks, contributing to the area reduction.

Fork seat construction:

Reduce FET distance:

Technology to shorten the distance between adjacent FETs to 10 nm with a forked sheet structure (an improved version of the nanosheet structure) (Lecture No. 23.1)

A technology that eliminates the increase in silicon area by placing embedded power supply wiring (BPR) directly under the transistor (Lecture No. 23.3)

A report pointing out that heat dissipation is a problem of the power supply network (BSPDN) on the backside of the wafer (Lecture No. 23.4)

Research and development of semiconductor devices:

“Reliability” occupies a very important position.

There are mainly two failure mechanisms that limit the long-term reliability (lifetime) of transistors.

One is Bias Temperature Instability (BTI),

Another is time-dependent dielectric breakdown (TDDB).

former:

Long-term voltage application causes threshold voltage fluctuation and mutual conductance reduction.

the latter:

Long-term voltage application causes insulation deterioration in the gate insulation film, leading to dielectric breakdown.

Imec’s BTI research results:

imec presented two research results on bias temperature instability (BTI) at IEDM 2022.

1st:

Result of method to improve BTI in next-generation silicon HKMG CMOS (Lecture No. 30.4)

PBTI for n-channel MOS FETs:

With oxygen treatment below 300℃,

It was shown that NBTI of p-channel MOS FET is improved by hydrogen treatment below 300℃.

2nd:

Presentation on BTI degradation measurement method for IGZO (indium-gallium-zinc oxide) channel TFT (thin-film transistor) (Lecture No. 30.1)

By measuring the current-voltage characteristics while irradiating light with different wavelengths, we grasped the BTI deterioration characteristics and constructed a highly accurate deterioration model.

Other Reliability Related:

Estimation of the cause of excessive 1/f noise generated by CMOS in cryogenic environments (Lecture No. 30.5),

On-resistance distribution by back barrier of GaN HEMT (Lecture No. 30.6),

A research result on electrostatic discharge (ESD) resistance of GaN HEMT (on Si substrate) (Lecture No. 30.7) was presented.

“Compound semiconductor”, “Sensing”, “Cryogenic CMOS circuit”, “Next generation process”

There were a total of 6 presentations.

Two are for compound semiconductors and one for sensing, and one for others.

What kind of research theme will Rapidus dispatch engineers to in the future?

The choice is interesting.

[Akira Fukuda’s front line in the semiconductor industry]

-PC Watch

https://pc.watch.impress.co.jp/docs/column/semicon/1466624.html

imec : la recherche de pointe sur les semi-conducteurs ouverte au public !

ーAnnoncé à l’IEDM (International Electron Devices Meeting)ー

ーRapidus développé conjointement avec l’imecー

Rapide :

Le 6 décembre 2022, un protocole de coopération a été signé avec l’imec de Belgique.

Basé sur MOC, nous visons à produire en masse des semi-conducteurs après la génération 2nm.

Aperçu du protocole de coopération :

Il est consultable sur le site du ministère de l’Economie, du Commerce et de l’Industrie (en date du 6 décembre).

La vue d’ensemble du MOC est intéressante à plusieurs égards.

La recherche conjointe sur les technologies élémentaires va de soi.

Il fait référence à la technologie d’exposition EUV.

Possibilité d’envoyer des ingénieurs de Rapidus à imec.

Élaborer conjointement une feuille de route R&D.

imec établira une équipe de recherche et développement au Japon.

La ligne de prototypes d’Imec :

ーExistence qui symbolise la taille de l’échelleー

Il s’agit d’une « ligne prototype pour wafers de 300 mm de diamètre, équipée des derniers équipements de fabrication ».

Un institut de recherche ne possède pas de chaîne de fabrication de semi-conducteurs capable de traiter des tranches de 300 mm de diamètre.

IEDM :

ーLa plus grande conférence internationale au monde sur la technologie des dispositifs semi-conducteurs et la technologie des procédésー

L’IEDM s’est tenu à San Francisco du 5 au 7 décembre.

l’imec a dévoilé 21 activités de recherche et développement.

Annonce des résultats de recherche d’Intel :

Le nombre de présentations à l’IEDM d’Intel était de 11 (3 invités, 8 généraux),

“Le nombre d’annonces imec est le double de celui d’Intel.”

Les derniers axes de recherche d’Imec :

ーDomaines de recherche annoncés par l’imec à l’IEDM 2022ー

“Une mémoire non volatile”

“Logique CMOS, transistors et câblage”

“fiabilité”

« Semi-conducteur composé »

“Sentir”

“Circuit cryogénique CMOS”

Une large gamme de “procédés de nouvelle génération”.

Mémoire ferroélectrique (FeRAM):

Condensateur ferroélectrique prototype à haute performance avec film ferroélectrique de dioxyde d’hafnium-zirconium dopé au lanthane (La: HZO) (Conférence n ° 6.4)

Le contrôle de l’interface par une couche germe d’oxyde de titane (TiO2) et une couche coiffe d’oxyde de niobium (Nb2O5) contribue à améliorer la qualité des films ferroélectriques.

Même après 10 11 cycles d’inversion de polarisation, la polarisation rémanente (2Pr) atteint 30 μC/cm 2 .

Mémoire magnétique (MRAM):

Mémoire magnétique prototype de type couple spin-orbite (SOT-MRAM) pouvant être lue et écrite sans champ magnétique externe (Conférence n ° 36.2)

L’intégration dans la logique CMOS est possible.

La cellule mémoire prototype a un temps de commutation court de 0,3ns.

La durée de vie du cycle de réécriture (estimation) dépasse 10 puissance 12.

Sélecteur pour point de croisement :

Nous avons présenté des résultats de recherche sur le mécanisme de variation de tension de seuil (Conférence n° 5.1) et les matériaux sélecteurs excluant les substances toxiques (Conférence n° 8.6).

-Conférence par un chercheur détaché de KIOXIA-

Dans ces deux présentations, les chercheurs détachés de KIOXIA à l’imec sont les auteurs principaux (c’est-à-dire les conférenciers).

Logique CMOS et transistors, câblage :

Pour la logique CMOS, les transistors et le câblage, des technologies permettant de réduire la surface du circuit et de raccourcir les dimensions du circuit sans compter sur la réduction de la taille du processus ont été présentées.

Tous sont des résultats de recherche pour le nœud technologique après 2 nm.

Circuit de base logique CMOS :

Cellule standard :

Pour la cellule standard, qui est le circuit de base de la logique CMOS, nous avons annoncé une technologie permettant de réduire la hauteur de la cellule en concevant une structure de câblage multicouche. (Conférence numéro 23.2)

La surface de cellule standard a été réduite de 21 % par rapport aux modèles conventionnels.

La hauteur de la cellule a été abaissée de 5 pistes à 4 pistes, contribuant à la réduction de la surface.

Construction du siège de fourche :

Réduisez la distance FET :

Technologie pour raccourcir la distance entre les FET adjacents à 10 nm avec une structure de feuille fourchue (une version améliorée de la structure de nanofeuille) (Conférence n° 23.1)

Une technologie qui élimine l’augmentation de la surface de silicium en plaçant le câblage d’alimentation intégré (BPR) directement sous le transistor (Conférence n ° 23.3)

Un rapport soulignant que la dissipation thermique est un problème du réseau d’alimentation (BSPDN) à l’arrière de la plaquette (Conférence n ° 23.4)

Recherche et développement de dispositifs semi-conducteurs :

La “fiabilité” occupe une place très importante.

Il existe principalement deux mécanismes de défaillance qui limitent la fiabilité à long terme (durée de vie) des transistors.

L’un est l’instabilité de la température de polarisation (BTI),

Un autre est le claquage diélectrique dépendant du temps (TDDB).

ancien:

L’application de tension à long terme provoque une fluctuation de la tension de seuil et une réduction mutuelle de la conductance.

le dernier:

L’application de tension à long terme provoque une détérioration de l’isolation dans le film d’isolation de grille, entraînant une panne diélectrique.

Résultats de la recherche BTI d’Imec :

imec a présenté deux résultats de recherche sur l’instabilité de température de biais (BTI) à l’IEDM 2022.

1er :

Résultat de la méthode d’amélioration du BTI dans le silicium HKMG CMOS de nouvelle génération (Conférence n° 30.4)

PBTI pour les MOS FET à canal n :

Avec un traitement à l’oxygène inférieur à 300℃,

Il a été démontré que le NBTI du MOS FET à canal p est amélioré par un traitement à l’hydrogène en dessous de 300℃.

2ème :

Présentation sur la méthode de mesure de la dégradation du BTI pour le canal IGZO (oxyde d’indium-gallium-zinc) TFT (transistor à couches minces) (Conférence n° 30.1)

En mesurant les caractéristiques courant-tension tout en irradiant la lumière avec différentes longueurs d’onde, nous avons saisi les caractéristiques de détérioration BTI et construit un modèle de détérioration très précis.

Autres liés à la fiabilité :

Estimation de la cause du bruit 1/f excessif généré par CMOS dans les environnements cryogéniques (Cours n° 30.5),

Répartition de la résistance à l’état passant par barrière arrière de GaN HEMT (Conférence n° 30.6),

Un résultat de recherche sur la résistance aux décharges électrostatiques (ESD) du GaN HEMT (sur substrat Si) (Conférence n° 30.7) a été présenté.

” Semi-conducteur composé “, ” Détection “, ” Circuit cryogénique CMOS “, ” Processus de nouvelle génération “

Il y avait un total de 6 présentations.

Deux sont pour les semi-conducteurs composés et un pour la détection, et un pour les autres.

Dans quel type de thème de recherche Rapidus détachera-t-il ses ingénieurs à l’avenir ?

Le choix est intéressant.

[Ligne de front d’Akira Fukuda dans l’industrie des semi-conducteurs]

-Montre PC

imec: Modernste Halbleiterforschung für die Öffentlichkeit zugänglich!

ーAnkündigung auf dem IEDM (International Electron Devices Meeting)ー

ーRapidus gemeinsam mit imec entwickeltー

Rapidus:

Am 6. Dezember 2022 wurde eine Kooperationsvereinbarung mit dem belgischen imec unterzeichnet.

Basierend auf MOC streben wir die Massenproduktion von Halbleitern nach der 2-nm-Generation an.

Übersicht über das Memorandum of Cooperation:

Es kann auf der Website des Ministeriums für Wirtschaft, Handel und Industrie eingesehen werden (vom 6. Dezember).

Die MOC-Übersicht ist in mehrfacher Hinsicht interessant.

Gemeinsame Forschung zu elementaren Technologien ist dabei selbstverständlich.

Es bezieht sich auf die EUV-Belichtungstechnologie.

Fähigkeit, Ingenieure von Rapidus zu imec zu schicken.

Formulieren Sie gemeinsam eine F&E-Roadmap.

imec wird ein Forschungs- und Entwicklungsteam in Japan aufbauen.

Prototypenlinie von Imec:

ーExistenz, die die Größe des Maßstabs symbolisiertー

Es handele sich um eine „Prototypenlinie für Wafer mit einem Durchmesser von 300 mm, ausgestattet mit modernster Fertigungstechnik“.

Ein Forschungsinstitut besitzt keine Halbleiterfertigungsstraße, die Wafer mit 300 mm Durchmesser handhaben kann.

IEDMs:

ーDie weltweit größte internationale Konferenz für Halbleitergerätetechnologie und Prozesstechnologieー

IEDM fand vom 5. bis 7. Dezember in San Francisco statt.

imec stellte 21 Forschungs- und Entwicklungsaktivitäten vor.

Ankündigung von Intel-Forschungsergebnissen:

Die Anzahl der Präsentationen bei Intels IEDM betrug 11 (3 eingeladene, 8 allgemeine),

“Die Zahl der imec-Ankündigungen ist doppelt so hoch wie die von Intel.”

Neueste Forschungsgebiete von Imec:

ーForschungsbereiche, die von imec auf der IEDM 2022 angekündigt wurdenー

“Nichtflüchtiger Speicher”

“CMOS-Logik, Transistoren und Verdrahtung”

“Verlässlichkeit”

“Verbindungshalbleiter”

“Sensing”

“Kryogene CMOS-Schaltung”

Ein breites Spektrum an „Prozessen der nächsten Generation“.

Ferroelektrischer Speicher (FeRAM):

Prototyp eines ferroelektrischen Hochleistungskondensators mit Lanthan-dotiertem Hafnium-Zirkoniumdioxid (La:HZO) ferroelektrischem Film (Vortrag Nr. 6.4)

Die Grenzflächenkontrolle durch eine Keimschicht aus Titanoxid (TiO2) und eine Deckschicht aus Nioboxid (Nb2O5) trägt zur Verbesserung der Qualität ferroelektrischer Filme bei.

Selbst nach 10 11 Zyklen der Polarisationsumkehr ist die remanente Polarisation (2Pr) so groß wie 30 &mgr;C/cm 2 .

Magnetspeicher (MRAM):

Prototyp eines Magnetspeichers vom Spin-Orbit-Torque-Typ (SOT-MRAM), der ohne externes Magnetfeld gelesen und beschrieben werden kann (Vortrag Nr. 36.2)

Eine Einbettung in CMOS-Logik ist möglich.

Die Prototyp-Speicherzelle hat eine kurze Schaltzeit von 0,3 ns.

Die Wiederschreibzykluslebensdauer (Schätzung) übersteigt 10 hoch 12. Potenz.

Selektor für Koppelpunkt:

Wir präsentierten Forschungsergebnisse zum Mechanismus der Schwellenspannungsvariation (Vortrag Nr. 5.1) und Selektormaterialien ohne toxische Substanzen (Vortrag Nr. 8.6).

-Vortrag eines von KIOXIA entsandten Forschers-

Bei diesen beiden Präsentationen sind von KIOXIA an das imec entsandte Forscher die Hauptautoren (dh Referenten).

CMOS-Logik und Transistoren, Beschaltung:

Für CMOS-Logik, -Transistoren und -Verdrahtung wurden Technologien zum Reduzieren der Schaltungsfläche und zum Verkürzen der Schaltungsabmessungen vorgestellt, ohne sich auf eine Reduzierung der Prozessgröße zu verlassen.

Allesamt Forschungsergebnisse für den Technologieknoten nach 2nm.

CMOS-Logik-Grundschaltung:

Standardzelle:

Für die Standardzelle, die die Grundschaltung der CMOS-Logik darstellt, haben wir eine Technologie angekündigt, um die Höhe der Zelle durch die Entwicklung einer mehrschichtigen Verdrahtungsstruktur zu reduzieren. (Vortragsnummer 23.2)

Die Standardzellenfläche wurde im Vergleich zu herkömmlichen Modellen um 21 % reduziert.

Die Zellenhöhe wurde von 5 Gleisen auf 4 Gleise abgesenkt, was zur Flächenreduzierung beitrug.

Gabelsitzkonstruktion:

FET-Abstand verringern:

Technologie zur Verkürzung des Abstands zwischen benachbarten FETs auf 10 nm mit einer gegabelten Blattstruktur (einer verbesserten Version der Nanoblattstruktur) (Vortrag Nr. 23.1)

Eine Technologie, die die Vergrößerung der Siliziumfläche eliminiert, indem eingebettete Stromversorgungsverdrahtung (BPR) direkt unter dem Transistor platziert wird (Vortrag Nr. 23.3)

Ein Bericht, der darauf hinweist, dass die Wärmeableitung ein Problem des Stromversorgungsnetzes (BSPDN) auf der Rückseite des Wafers ist (Vortrag Nr. 23.4)

Forschung und Entwicklung von Halbleiterbauelementen:

„Zuverlässigkeit“ nimmt eine sehr wichtige Stellung ein.

Es gibt hauptsächlich zwei Ausfallmechanismen, die die langfristige Zuverlässigkeit (Lebensdauer) von Transistoren begrenzen.

Einer ist Bias Temperature Instability (BTI),

Ein weiterer ist der zeitabhängige dielektrische Durchbruch (TDDB).

ehemalige:

Langfristiges Anlegen einer Spannung verursacht Schwankungen der Schwellenspannung und eine Verringerung der gegenseitigen Konduktanz.

letzteres:

Das Anlegen einer Langzeitspannung verursacht eine Isolationsverschlechterung im Gate-Isolationsfilm, was zu einem Durchschlag des Dielektrikums führt.

BTI-Forschungsergebnisse von Imec:

imec präsentierte auf der IEDM 2022 zwei Forschungsergebnisse zur Bias-Temperaturinstabilität (BTI).

1:

Ergebnis der Methode zur Verbesserung von BTI in Silizium-HKMG-CMOS der nächsten Generation (Vortrag Nr. 30.4)

PBTI für n-Kanal-MOSFETs:

Mit Sauerstoffbehandlung unter 300℃,

Es wurde gezeigt, dass der NBTI von p-Kanal-MOS-FETs durch eine Wasserstoffbehandlung unter 300 ° C verbessert wird.

2.:

Präsentation zum BTI-Degradationsmessverfahren für IGZO (Indium-Gallium-Zink-Oxid)-Kanal-TFT (Dünnschichttransistor) (Vortrag Nr. 30.1)

Durch Messen der Strom-Spannungs-Charakteristika bei Einstrahlung von Licht mit unterschiedlichen Wellenlängen haben wir die BTI-Verschlechterungscharakteristika erfasst und ein hochgenaues Verschlechterungsmodell konstruiert.

Andere Zuverlässigkeit bezogen:

Abschätzung der Ursache für übermäßiges 1/f-Rauschen, das von CMOS in kryogenen Umgebungen erzeugt wird (Vortrag Nr. 30.5),

On-Resistance Distribution by Back Barrier of GaN HEMT (Vortrag Nr. 30.6),

Ein Forschungsergebnis zur Beständigkeit von GaN-HEMT (auf Si-Substrat) gegen elektrostatische Entladung (ESD) (Vortrag Nr. 30.7) wurde vorgestellt.

“Verbindungshalbleiter”, “Sensorik”, “Kryogene CMOS-Schaltung”, “Prozess der nächsten Generation”

Es gab insgesamt 6 Präsentationen.

Zwei sind für Verbindungshalbleiter und einer für die Sensorik und einer für andere.

Zu welcher Art von Forschungsthema wird Rapidus in Zukunft Ingenieure entsenden?

Die Wahl ist interessant.

[Akira Fukudas Frontlinie in der Halbleiterindustrie]

-PC-Uhr