imec:最先進的半導體研究向公眾開放!

ー在IEDM(國際電子器件會議)上發表ー

ー與imec共同開發的Rapidusー

急速:

2022年12月6日,與比利時imec簽署合作備忘錄。

基於MOC,我們的目標是量產2nm後的半導體。

合作備忘錄概覽:

可以在經濟產業省網站(12 月 6 日)上查看。

MOC 概述在幾個方面很有趣。

共同研究基礎技術是理所當然的事情。

指的是EUV曝光技術。

能夠從 Rapidus 派遣工程師到 imec。

共同製定研發路線圖。

imec將在日本建立研發團隊。

Imec 的原型線:

ー象徵規模大小的存在ー

這是一條“配備最新製造設備的直徑為 300 毫米的晶圓原型生產線”。

研究機構不擁有能夠處理 300mm 直徑晶圓的半導體生產線。

IEDM:

ー全球最大的半導體器件技術與工藝技術國際會議ー

IEDM於12月5日至7日在舊金山舉行。

imec公佈了21項研發活動。

英特爾研究成果公佈:

英特爾 IEDM 的演講次數為 11 次(3 次受邀,8 次一般),

“imec 公告的數量是英特爾的兩倍。”

Imec最新研究領域:

ーIMEC在IEDM 2022上公佈的研究領域ー

“非易失性存儲器”

“CMOS 邏輯、晶體管和佈線”

“可靠性”

《化合物半導體》

“感應”

《低溫CMOS電路》

範圍廣泛的“下一代工藝”。

鐵電存儲器 (FeRAM):

具有鑭摻雜二氧化鉿鋯 (La:HZO) 鐵電薄膜的高性能鐵電電容器原型(第 6.4 講)

通過氧化鈦 (TiO2) 種子層和氧化鈮 (Nb2O5) 覆蓋層進行界面控制有助於提高鐵電薄膜的質量。

即使在 10 11 個極化反轉循環之後,剩餘極化 (2Pr) 仍高達 30 μC/cm 2 。

磁存儲器(MRAM):

無需外部磁場即可讀寫的自旋軌道扭矩型磁存儲器(SOT-MRAM)原型(第36.2講)

可以嵌入 CMOS 邏輯。

原型存儲單元具有 0.3ns 的短切換時間。

重寫循環壽命(估計)超過 10 的 12 次方。

交叉點選擇器:

我們介紹了閾值電壓變化機制(第 5.1 講)和排除有毒物質的選擇器材料(第 8.6 講)的研究結果。

-鎧俠派遣研究人員的演講-

在這兩個演講中,鎧俠派往 imec 的研究人員都是主要作者(即演講者)。

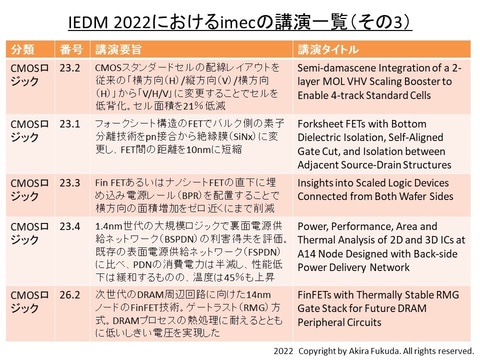

CMOS邏輯和晶體管,佈線:

對於 CMOS 邏輯、晶體管和佈線,提出了在不依賴工藝尺寸減小的情況下減小電路面積和縮短電路尺寸的技術。

都是針對2nm之後技術節點的研究成果。

CMOS邏輯基本電路:

標準電池:

對於作為 CMOS 邏輯的基本電路的標准單元,我們發布了一項通過設計多層佈線結構來降低單元高度的技術。 (第 23.2 講)

與傳統型號相比,標准單元面積減少了 21%。

單元高度從 5 個軌道降低到 4 個軌道,有助於減少面積。

叉座結構:

減少 FET 距離:

利用叉狀片結構(納米片結構的改進版)將相鄰 FET 之間的距離縮短至 10 nm 的技術(第 23.1 講)

一種通過將嵌入式電源佈線(BPR)直接置於晶體管下方來消除矽面積增加的技術(第23.3講)

一篇報告指出散熱是晶圓背面供電網絡(BSPDN)的問題(第23.4講)

半導體器件研發:

“可靠性”佔據著非常重要的位置。

主要有兩種失效機制限制了晶體管的長期可靠性(壽命)。

一是偏置溫度不穩定性 (BTI),

另一個是時間相關的電介質擊穿 (TDDB)。

以前的:

長期施加電壓會導致閾值電壓波動和互導降低。

後者:

長期施加電壓會導致柵極絕緣膜的絕緣劣化,從而導致絕緣擊穿。

Imec的BTI研究成果:

imec 在 IEDM 2022 上展示了兩項關於偏置溫度不穩定性 (BTI) 的研究成果。

第一:

提高下一代矽HKMG CMOS BTI方法的結果(第30.4講)

用於 n 溝道 MOS FET 的 PBTI:

300℃以下氧處理,

結果表明,300℃以下的氫處理改善了p溝道MOS FET的NBTI。

第二:

IGZO(氧化銦鎵鋅)溝道TFT(薄膜晶體管)的BTI劣化測量方法介紹(第30.1講)

通過在照射不同波長的光的同時測量電流-電壓特性,我們掌握了 BTI 劣化特性並構建了高精度劣化模型。

其他可靠性相關:

低溫環境下CMOS產生過大1/f噪聲的原因估計(第30.5講),

GaN HEMT 背勢壘的導通電阻分佈(第 30.6 講),

介紹了 GaN HEMT(在 Si 襯底上)的靜電放電 (ESD) 電阻研究結果(第 30.7 講)。

《化合物半導體》、《傳感》、《低溫CMOS電路》、《下一代工藝》

共有 6 場演講。

兩種用於化合物半導體,一種用於傳感,另一種用於其他。

Rapidus 未來將派遣工程師進行什麼樣的研究課題?

這個選擇很有趣。

【福田彰在半導體行業的第一線】

-電腦手錶

https://pc.watch.impress.co.jp/docs/column/semicon/1466624.html

imec : la recherche de pointe sur les semi-conducteurs ouverte au public !

ーAnnoncé à l’IEDM (International Electron Devices Meeting)ー

ーRapidus développé conjointement avec l’imecー

Rapide :

Le 6 décembre 2022, un protocole de coopération a été signé avec l’imec de Belgique.

Basé sur MOC, nous visons à produire en masse des semi-conducteurs après la génération 2nm.

Aperçu du protocole de coopération :

Il est consultable sur le site du ministère de l’Economie, du Commerce et de l’Industrie (en date du 6 décembre).

La vue d’ensemble du MOC est intéressante à plusieurs égards.

La recherche conjointe sur les technologies élémentaires va de soi.

Il fait référence à la technologie d’exposition EUV.

Possibilité d’envoyer des ingénieurs de Rapidus à imec.

Élaborer conjointement une feuille de route R&D.

imec établira une équipe de recherche et développement au Japon.

La ligne de prototypes d’Imec :

ーExistence qui symbolise la taille de l’échelleー

Il s’agit d’une « ligne prototype pour wafers de 300 mm de diamètre, équipée des derniers équipements de fabrication ».

Un institut de recherche ne possède pas de chaîne de fabrication de semi-conducteurs capable de traiter des tranches de 300 mm de diamètre.

IEDM :

ーLa plus grande conférence internationale au monde sur la technologie des dispositifs semi-conducteurs et la technologie des procédésー

L’IEDM s’est tenu à San Francisco du 5 au 7 décembre.

l’imec a dévoilé 21 activités de recherche et développement.

Annonce des résultats de recherche d’Intel :

Le nombre de présentations à l’IEDM d’Intel était de 11 (3 invités, 8 généraux),

“Le nombre d’annonces imec est le double de celui d’Intel.”

Les derniers axes de recherche d’Imec :

ーDomaines de recherche annoncés par l’imec à l’IEDM 2022ー

“Une mémoire non volatile”

“Logique CMOS, transistors et câblage”

“fiabilité”

« Semi-conducteur composé »

“Sentir”

“Circuit cryogénique CMOS”

Une large gamme de “procédés de nouvelle génération”.

Mémoire ferroélectrique (FeRAM):

Condensateur ferroélectrique prototype à haute performance avec film ferroélectrique de dioxyde d’hafnium-zirconium dopé au lanthane (La: HZO) (Conférence n ° 6.4)

Le contrôle de l’interface par une couche germe d’oxyde de titane (TiO2) et une couche coiffe d’oxyde de niobium (Nb2O5) contribue à améliorer la qualité des films ferroélectriques.

Même après 10 11 cycles d’inversion de polarisation, la polarisation rémanente (2Pr) atteint 30 μC/cm 2 .

Mémoire magnétique (MRAM):

Mémoire magnétique prototype de type couple spin-orbite (SOT-MRAM) pouvant être lue et écrite sans champ magnétique externe (Conférence n ° 36.2)

L’intégration dans la logique CMOS est possible.

La cellule mémoire prototype a un temps de commutation court de 0,3ns.

La durée de vie du cycle de réécriture (estimation) dépasse 10 puissance 12.

Sélecteur pour point de croisement :

Nous avons présenté des résultats de recherche sur le mécanisme de variation de tension de seuil (Conférence n° 5.1) et les matériaux sélecteurs excluant les substances toxiques (Conférence n° 8.6).

-Conférence par un chercheur détaché de KIOXIA-

Dans ces deux présentations, les chercheurs détachés de KIOXIA à l’imec sont les auteurs principaux (c’est-à-dire les conférenciers).

Logique CMOS et transistors, câblage :

Pour la logique CMOS, les transistors et le câblage, des technologies permettant de réduire la surface du circuit et de raccourcir les dimensions du circuit sans compter sur la réduction de la taille du processus ont été présentées.

Tous sont des résultats de recherche pour le nœud technologique après 2 nm.

Circuit de base logique CMOS :

Cellule standard :

Pour la cellule standard, qui est le circuit de base de la logique CMOS, nous avons annoncé une technologie permettant de réduire la hauteur de la cellule en concevant une structure de câblage multicouche. (Conférence numéro 23.2)

La surface de cellule standard a été réduite de 21 % par rapport aux modèles conventionnels.

La hauteur de la cellule a été abaissée de 5 pistes à 4 pistes, contribuant à la réduction de la surface.

Construction du siège de fourche :

Réduisez la distance FET :

Technologie pour raccourcir la distance entre les FET adjacents à 10 nm avec une structure de feuille fourchue (une version améliorée de la structure de nanofeuille) (Conférence n° 23.1)

Une technologie qui élimine l’augmentation de la surface de silicium en plaçant le câblage d’alimentation intégré (BPR) directement sous le transistor (Conférence n ° 23.3)

Un rapport soulignant que la dissipation thermique est un problème du réseau d’alimentation (BSPDN) à l’arrière de la plaquette (Conférence n ° 23.4)

Recherche et développement de dispositifs semi-conducteurs :

La “fiabilité” occupe une place très importante.

Il existe principalement deux mécanismes de défaillance qui limitent la fiabilité à long terme (durée de vie) des transistors.

L’un est l’instabilité de la température de polarisation (BTI),

Un autre est le claquage diélectrique dépendant du temps (TDDB).

ancien:

L’application de tension à long terme provoque une fluctuation de la tension de seuil et une réduction mutuelle de la conductance.

le dernier:

L’application de tension à long terme provoque une détérioration de l’isolation dans le film d’isolation de grille, entraînant une panne diélectrique.

Résultats de la recherche BTI d’Imec :

imec a présenté deux résultats de recherche sur l’instabilité de température de biais (BTI) à l’IEDM 2022.

1er :

Résultat de la méthode d’amélioration du BTI dans le silicium HKMG CMOS de nouvelle génération (Conférence n° 30.4)

PBTI pour les MOS FET à canal n :

Avec un traitement à l’oxygène inférieur à 300℃,

Il a été démontré que le NBTI du MOS FET à canal p est amélioré par un traitement à l’hydrogène en dessous de 300℃.

2ème :

Présentation sur la méthode de mesure de la dégradation du BTI pour le canal IGZO (oxyde d’indium-gallium-zinc) TFT (transistor à couches minces) (Conférence n° 30.1)

En mesurant les caractéristiques courant-tension tout en irradiant la lumière avec différentes longueurs d’onde, nous avons saisi les caractéristiques de détérioration BTI et construit un modèle de détérioration très précis.

Autres liés à la fiabilité :

Estimation de la cause du bruit 1/f excessif généré par CMOS dans les environnements cryogéniques (Cours n° 30.5),

Répartition de la résistance à l’état passant par barrière arrière de GaN HEMT (Conférence n° 30.6),

Un résultat de recherche sur la résistance aux décharges électrostatiques (ESD) du GaN HEMT (sur substrat Si) (Conférence n° 30.7) a été présenté.

” Semi-conducteur composé “, ” Détection “, ” Circuit cryogénique CMOS “, ” Processus de nouvelle génération “

Il y avait un total de 6 présentations.

Deux sont pour les semi-conducteurs composés et un pour la détection, et un pour les autres.

Dans quel type de thème de recherche Rapidus détachera-t-il ses ingénieurs à l’avenir ?

Le choix est intéressant.

[Ligne de front d’Akira Fukuda dans l’industrie des semi-conducteurs]

-Montre PC

imec: Modernste Halbleiterforschung für die Öffentlichkeit zugänglich!

ーAnkündigung auf dem IEDM (International Electron Devices Meeting)ー

ーRapidus gemeinsam mit imec entwickeltー

Rapidus:

Am 6. Dezember 2022 wurde eine Kooperationsvereinbarung mit dem belgischen imec unterzeichnet.

Basierend auf MOC streben wir die Massenproduktion von Halbleitern nach der 2-nm-Generation an.

Übersicht über das Memorandum of Cooperation:

Es kann auf der Website des Ministeriums für Wirtschaft, Handel und Industrie eingesehen werden (vom 6. Dezember).

Die MOC-Übersicht ist in mehrfacher Hinsicht interessant.

Gemeinsame Forschung zu elementaren Technologien ist dabei selbstverständlich.

Es bezieht sich auf die EUV-Belichtungstechnologie.

Fähigkeit, Ingenieure von Rapidus zu imec zu schicken.

Formulieren Sie gemeinsam eine F&E-Roadmap.

imec wird ein Forschungs- und Entwicklungsteam in Japan aufbauen.

Prototypenlinie von Imec:

ーExistenz, die die Größe des Maßstabs symbolisiertー

Es handele sich um eine „Prototypenlinie für Wafer mit einem Durchmesser von 300 mm, ausgestattet mit modernster Fertigungstechnik“.

Ein Forschungsinstitut besitzt keine Halbleiterfertigungsstraße, die Wafer mit 300 mm Durchmesser handhaben kann.

IEDMs:

ーDie weltweit größte internationale Konferenz für Halbleitergerätetechnologie und Prozesstechnologieー

IEDM fand vom 5. bis 7. Dezember in San Francisco statt.

imec stellte 21 Forschungs- und Entwicklungsaktivitäten vor.

Ankündigung von Intel-Forschungsergebnissen:

Die Anzahl der Präsentationen bei Intels IEDM betrug 11 (3 eingeladene, 8 allgemeine),

“Die Zahl der imec-Ankündigungen ist doppelt so hoch wie die von Intel.”

Neueste Forschungsgebiete von Imec:

ーForschungsbereiche, die von imec auf der IEDM 2022 angekündigt wurdenー

“Nichtflüchtiger Speicher”

“CMOS-Logik, Transistoren und Verdrahtung”

“Verlässlichkeit”

“Verbindungshalbleiter”

“Sensing”

“Kryogene CMOS-Schaltung”

Ein breites Spektrum an „Prozessen der nächsten Generation“.

Ferroelektrischer Speicher (FeRAM):

Prototyp eines ferroelektrischen Hochleistungskondensators mit Lanthan-dotiertem Hafnium-Zirkoniumdioxid (La:HZO) ferroelektrischem Film (Vortrag Nr. 6.4)

Die Grenzflächenkontrolle durch eine Keimschicht aus Titanoxid (TiO2) und eine Deckschicht aus Nioboxid (Nb2O5) trägt zur Verbesserung der Qualität ferroelektrischer Filme bei.

Selbst nach 10 11 Zyklen der Polarisationsumkehr ist die remanente Polarisation (2Pr) so groß wie 30 &mgr;C/cm 2 .

Magnetspeicher (MRAM):

Prototyp eines Magnetspeichers vom Spin-Orbit-Torque-Typ (SOT-MRAM), der ohne externes Magnetfeld gelesen und beschrieben werden kann (Vortrag Nr. 36.2)

Eine Einbettung in CMOS-Logik ist möglich.

Die Prototyp-Speicherzelle hat eine kurze Schaltzeit von 0,3 ns.

Die Wiederschreibzykluslebensdauer (Schätzung) übersteigt 10 hoch 12. Potenz.

Selektor für Koppelpunkt:

Wir präsentierten Forschungsergebnisse zum Mechanismus der Schwellenspannungsvariation (Vortrag Nr. 5.1) und Selektormaterialien ohne toxische Substanzen (Vortrag Nr. 8.6).

-Vortrag eines von KIOXIA entsandten Forschers-

Bei diesen beiden Präsentationen sind von KIOXIA an das imec entsandte Forscher die Hauptautoren (dh Referenten).

CMOS-Logik und Transistoren, Beschaltung:

Für CMOS-Logik, -Transistoren und -Verdrahtung wurden Technologien zum Reduzieren der Schaltungsfläche und zum Verkürzen der Schaltungsabmessungen vorgestellt, ohne sich auf eine Reduzierung der Prozessgröße zu verlassen.

Allesamt Forschungsergebnisse für den Technologieknoten nach 2nm.

CMOS-Logik-Grundschaltung:

Standardzelle:

Für die Standardzelle, die die Grundschaltung der CMOS-Logik darstellt, haben wir eine Technologie angekündigt, um die Höhe der Zelle durch die Entwicklung einer mehrschichtigen Verdrahtungsstruktur zu reduzieren. (Vortragsnummer 23.2)

Die Standardzellenfläche wurde im Vergleich zu herkömmlichen Modellen um 21 % reduziert.

Die Zellenhöhe wurde von 5 Gleisen auf 4 Gleise abgesenkt, was zur Flächenreduzierung beitrug.

Gabelsitzkonstruktion:

FET-Abstand verringern:

Technologie zur Verkürzung des Abstands zwischen benachbarten FETs auf 10 nm mit einer gegabelten Blattstruktur (einer verbesserten Version der Nanoblattstruktur) (Vortrag Nr. 23.1)

Eine Technologie, die die Vergrößerung der Siliziumfläche eliminiert, indem eingebettete Stromversorgungsverdrahtung (BPR) direkt unter dem Transistor platziert wird (Vortrag Nr. 23.3)

Ein Bericht, der darauf hinweist, dass die Wärmeableitung ein Problem des Stromversorgungsnetzes (BSPDN) auf der Rückseite des Wafers ist (Vortrag Nr. 23.4)

Forschung und Entwicklung von Halbleiterbauelementen:

„Zuverlässigkeit“ nimmt eine sehr wichtige Stellung ein.

Es gibt hauptsächlich zwei Ausfallmechanismen, die die langfristige Zuverlässigkeit (Lebensdauer) von Transistoren begrenzen.

Einer ist Bias Temperature Instability (BTI),

Ein weiterer ist der zeitabhängige dielektrische Durchbruch (TDDB).

ehemalige:

Langfristiges Anlegen einer Spannung verursacht Schwankungen der Schwellenspannung und eine Verringerung der gegenseitigen Konduktanz.

letzteres:

Das Anlegen einer Langzeitspannung verursacht eine Isolationsverschlechterung im Gate-Isolationsfilm, was zu einem Durchschlag des Dielektrikums führt.

BTI-Forschungsergebnisse von Imec:

imec präsentierte auf der IEDM 2022 zwei Forschungsergebnisse zur Bias-Temperaturinstabilität (BTI).

1:

Ergebnis der Methode zur Verbesserung von BTI in Silizium-HKMG-CMOS der nächsten Generation (Vortrag Nr. 30.4)

PBTI für n-Kanal-MOSFETs:

Mit Sauerstoffbehandlung unter 300℃,

Es wurde gezeigt, dass der NBTI von p-Kanal-MOS-FETs durch eine Wasserstoffbehandlung unter 300 ° C verbessert wird.

2.:

Präsentation zum BTI-Degradationsmessverfahren für IGZO (Indium-Gallium-Zink-Oxid)-Kanal-TFT (Dünnschichttransistor) (Vortrag Nr. 30.1)

Durch Messen der Strom-Spannungs-Charakteristika bei Einstrahlung von Licht mit unterschiedlichen Wellenlängen haben wir die BTI-Verschlechterungscharakteristika erfasst und ein hochgenaues Verschlechterungsmodell konstruiert.

Andere Zuverlässigkeit bezogen:

Abschätzung der Ursache für übermäßiges 1/f-Rauschen, das von CMOS in kryogenen Umgebungen erzeugt wird (Vortrag Nr. 30.5),

On-Resistance Distribution by Back Barrier of GaN HEMT (Vortrag Nr. 30.6),

Ein Forschungsergebnis zur Beständigkeit von GaN-HEMT (auf Si-Substrat) gegen elektrostatische Entladung (ESD) (Vortrag Nr. 30.7) wurde vorgestellt.

“Verbindungshalbleiter”, “Sensorik”, “Kryogene CMOS-Schaltung”, “Prozess der nächsten Generation”

Es gab insgesamt 6 Präsentationen.

Zwei sind für Verbindungshalbleiter und einer für die Sensorik und einer für andere.

Zu welcher Art von Forschungsthema wird Rapidus in Zukunft Ingenieure entsenden?

Die Wahl ist interessant.

[Akira Fukudas Frontlinie in der Halbleiterindustrie]

-PC-Uhr