TSMC:産総研に評価ライン構築:3DIC研究開発センター(動画):

TSMC: Evaluation line at AIST: 3DIC R & D Center:

台积电:AIST评估线建设:3DIC研发中心

ー日本の20社、次世代半導体技術開発ー

今回採択が発表されたのは、「先端半導体製造技術の開発」

「高性能コンピューティング向け実装技術」を、TSMCジャパン・3DIC研究開発センターが受託した。

共同実施企業:

材料メーカーでは、

旭化成、

イビデン、

JSR、

昭和電工マテリアルズ、

信越化学工業、

新光電気工業、

住友化学、

積水化学工業、

東京応化工業、

長瀬産業、

日東電工、

日本電気硝子、

富士フイルム、

三井化学が参加している。装置メーカーでは、

キーエンス、

芝浦メカトロニクス、

島津製作所、

昭和電工、

ディスコ、

東レエンジニアリング、

日東電工、

日立ハイテクが参加する。大学・研究機関では、

産業技術総合研究所、

先端システム技術研究組合(RaaS)、

東京大学が参画する。3Dパッケージ技術確立の実現:

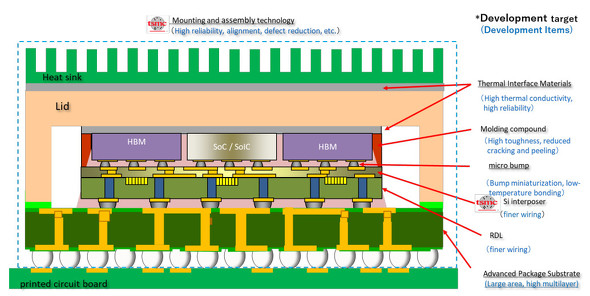

半導体デバイスの集積化と高性能化を実現する3Dパッケージ技術確立に取り組む。

- 基板上実装技術を中心に、

- 新加工技術、基板材料、接合プロセス、

- 新規の接合技術、計測技術など、

上記を組み合わせ、開発を進める。

TSMCジャパン:

- TSMCジャパンの3DIC研究開発センターが、

- 産業技術総合研究所のクリーンルーム内に、

- プロセスラインを構築し評価・検証を進めていく。

エッジコンピューティング実装技術:

先端システム技術研究組合(RaaS)と、

ソニーセミコンダクタソリューションズが受託した。先端システム技術研究組合:

事業テーマは、ダイレクト接合3D積層技術開発である。

- Cu-Cuの低温ハイブリッド接合によるWoW(Wafer on Wafer)接合技術と、

- CoW(Chip on Wafer)接合技術の構築とその実装化に取り組む。

産業技術総合研究所、

SCREENホールディングス、

ダイキン工業、

富士フイルム、

パナソニックスマートファクトリ、

東京大学、上記が、共同実施者として参加する。

ソニーセミコンダクタソリューションズ:

事業テーマは、ポスト5Gエッジコンピューティング半導体の3D積層要素技術研究開発だ。

- イメージセンサー積層技術において、

- 積層モジュールの基本特性、

- ピッチサイズ目標を年度ごとに設定し、

半導体製造プロセスの要素技術を確立する。

実装共通基盤技術の開発:

昭和電工マテリアルズと住友ベークライトが受託している。

昭和電工マテリアルズ:

事業テーマは、最先端パッケージ評価プラットフォーム創成だ。

- 基板、装置、材料メーカーのコンソーシアムで、

- 評価プラットフォームを設置。

- 次世代半導体パッケージを評価し、

基板、装置、材料の開発を行う。

味の素ファインテクノ、

上村工業、

荏原製作所、

新川、

新光電気工業、

大日本印刷、

ディスコ、

東京応化工業、

TOWA、

ナミックス、

パナソニックスマートファクトリー、

ヤマハロボティクスホールディングス、上記が、共同実施企業として参加する。

住友ベークライト:

事業テーマは、次世代情報通信向け先端パッケージの材料開発としている。

- 3次元実装密度向上において重要となる

- ウエハーレベルパッケージ向け封止材、

- アンテナ向け封止材、

再配線用感光材のファインピッチ対応技術を開発する。

FAニュース – MONOist

https://monoist.atmarkit.co.jp/mn/articles/2106/01/news065.html

産総研:3DIC実装技術の共同研究を開始

ー先端半導体の後工程技術開発拠点がつくばセンターにー

TSMCジャパン:

TSMCジャパンの3DIC研究開発センターは、3DIC実装のための新材料・新プロセス技術開発に関する共同研究をつくばセンターで、実施します。

3DIC 研究開発センター:

産総研および日本国内企業の新材料、

プロセス技術開発を評価・検証するため、

研究開発用パイロットラインを、

産総研つくば西事業所の高機能IoTデバイス研究開発棟に構築します。