DNP:ナノインプリントリソグラフィ:5nmノードに対応(動画):

DNP: Nanoimprint lithography: Supports 5nm node:

DNP:纳米压印光刻:支持 5nm 节点

ー従来型リソグラフィ技術の現像工程が不要ー

大日本印刷(DNP):

「第12回 高機能素材Week」(2021年12月8~10日、幕張メッセ)に出展。

カーボンニュートラルなど、環境負荷低減への事例を紹介。

ーDNPナノインプリントリソグラフィ(NIL)を展示ー

脱炭素社会の技術:

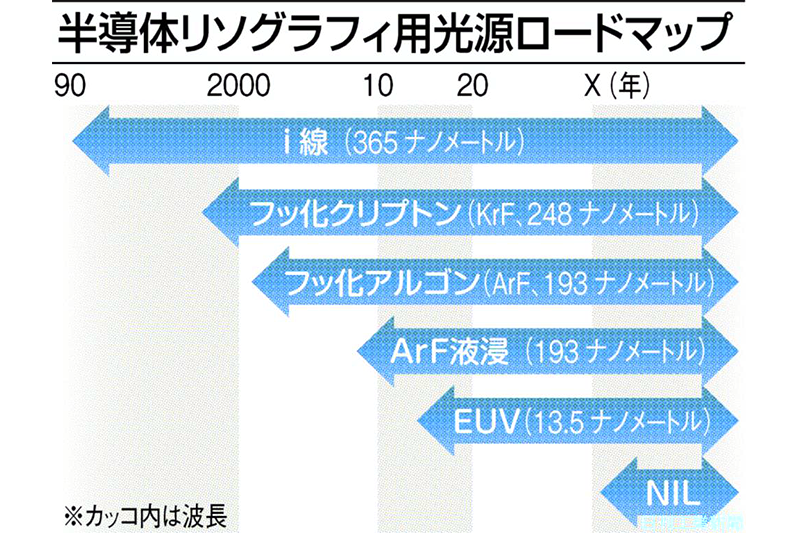

DNPナノインプリントリソグラフィによる、半導体製造向け超微細加工技術だ。

NILとは:

「基板材料に押し当てて、nm単位の超微細な凹凸を転写する技術」のこと。

「回路パターン用テンプレート(版の部分)の技術」が基になっている。

2003年

同社は2003年からNIL開発を開始。2015年

2015年に、NILの量産を開始。2021年

同社とキヤノン、キオクシアの3社が協力、「その技術を半導体製造における微細パターン形成に適用できる」ようにした。DNP:

これまでに培った「回路パターン用テンプレート製作技術」を提供。キヤノン:

回路パターン基板に、「詳細に転写するインプリント装置技術」を担う。キオクシア:

基板上のパターンを、「精密加工する半導体製造技術」を担う。5nmノードプロセス対応:

この技術は、「5nmノード世代の半導体製造プロセスにも対応可能」だ。

DNPのNIL:

「従来のリソグラフィ技術で使う現像工程」が不要となる。

「製造プロセスにおける大幅な低消費電力化」が可能。

それにより、半導体製造のカーボンニュートラルに貢献。

日経クロステック(xTECH)

https://xtech.nikkei.com/atcl/nxt/news/18/11907/

大日印・キオクシア・キヤノンが開発する「NIL」

ー半導体製造消費電力が10分の1ー

大日本印刷

キオクシアホールディングス、

キヤノン、共同で開発を進めるナノインプリントリソグラフィ(NIL)

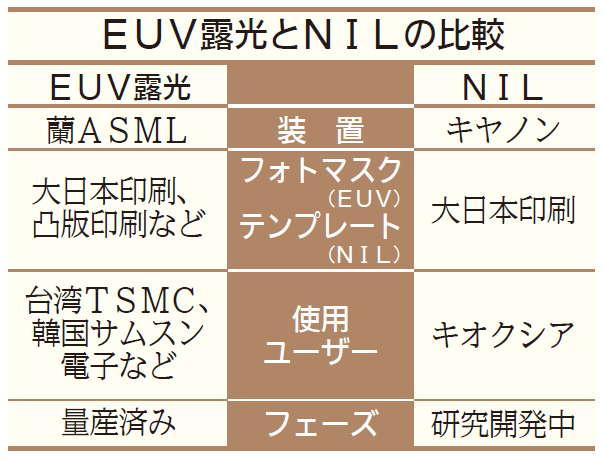

NILでの半導体製造:

「EUV露光と比べ、消費電力を10分の1に抑制できること」を明らかにした。

NILは量産利用までに課題が多いが、現在、最先端の回路線幅形成に成功。

NILとは:

NILは、型をウエハーに押しつけて微細な回路パターンを形成する。

NILは、技術開発用で回路線幅5ナノメートルノードまで対応可能という。

消費電力が10分の1:

大日本印刷は装置の仕様値による内部シミュレーションを2021年春に実施。

回路形成工程の1ウエハー当たり消費電力を発表。

「EUV露光使用時と比較し、10分の1にできること」が分かった。

ニュースイッチ