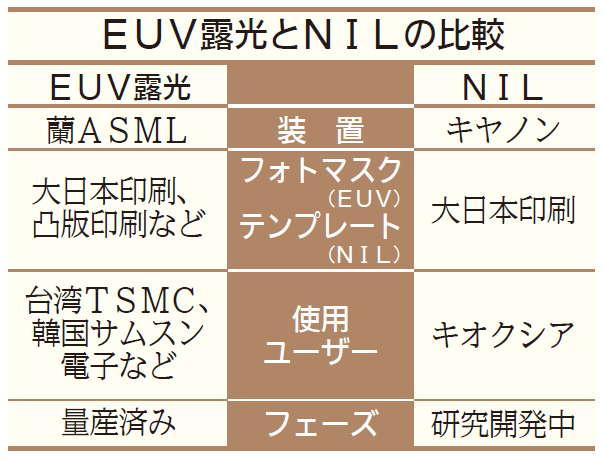

DNP:纳米压印光刻:支持 5nm 节点

-无需传统光刻技术的开发过程-

大日本印刷 (DNP):

参加“第12届高性能材料周”(2021年12月8-10日,幕张展览馆)。

介绍减少环境影响的例子,例如碳中和。

-展出 DNP 纳米压印光刻 (NIL)-

无碳社会技术:

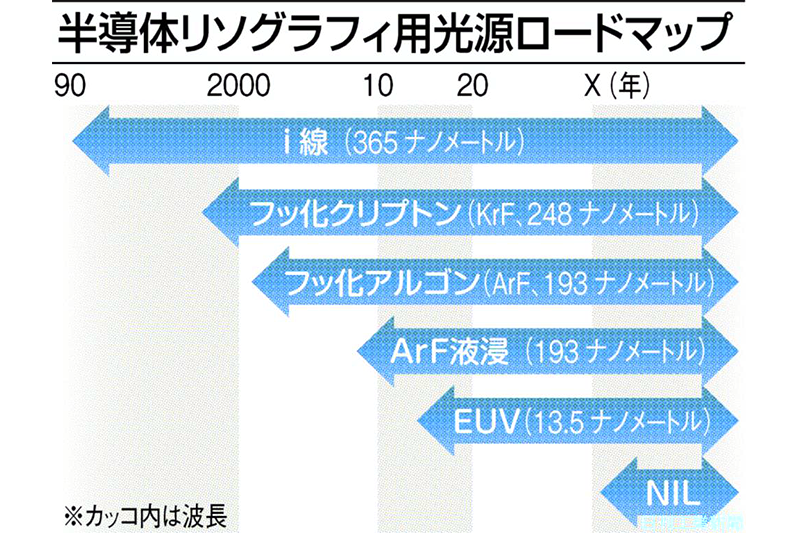

DNP纳米压印光刻技术是一种用于半导体制造的超精细加工技术。

什么是零:

“通过压在基板材料上以纳米为单位转移超细不规则性的技术”。

它基于“电路图案模板(板部分)技术”。

2003年

该公司于 2003 年开始开发 NIL。

2015年

2015年开始量产NIL。

2021年

该公司、佳能和铠侠已经合作,使“将该技术应用于半导体制造中的精细图案形成”成为可能。

DNP:

我们提供迄今为止所培养的“电路图案的模板制造技术”。

佳能:

负责“详细转移的压印装置技术”到电路图案板上。

铠侠:

负责基板上图案的“精密加工半导体制造技术”。

5nm节点工艺支持:

该技术“与 5nm 节点代半导体制造工艺兼容”。

DNP的零:

“传统光刻技术中使用的开发过程”变得没有必要。

“制造过程中的显着低功耗”是可能的。

这有助于半导体制造中的碳中和。

日经交叉技术 (xTECH)

https://xtech.nikkei.com/atcl/nxt/news/18/11907/

大日本印刷、铠侠、佳能共同开发的“NIL”

-半导体制造功耗是1/10-

大日本印刷

铠侠控股,

佳能,

正在联合开发的纳米压印光刻 (NIL)

NIL 的半导体制造:

澄清“与EUV曝光相比,功耗可降低至1/10”。

NIL在量产前存在诸多问题,但目前已成功形成最先进的电路线宽。

什么是零:

NIL 将模具压在晶片上以形成精细的电路图案。

NIL 用于技术开发,最多可处理 5 纳米节点电路线宽。

功耗为1/10

Dai Nippon Printing 于 2021 年春季根据设备的规格进行了内部模拟。

公布的电路形成过程中每片晶圆的功耗。

发现“与使用EUV曝光的情况相比,可以减少到1/10”。

新开关