2nm Next Generation Transistor: Developed Low Contact Resistance Technology!

ーAIST: Realization of higher performance in 2nm logic semiconductorsー

ーJapan-Taiwan: Build 2nm Si/Ge heterogeneous channel integration platformー

AIST

Tokyo Metropolitan University

The research group has developed a “low contact resistance technology that improves the performance of n-type MoS transistors.”

It can contribute to improving the performance of next-generation logic semiconductors.

Next-generation transistors beyond 2nm:

As a semiconductor material for the channel,

MoS2 (molybdenum disulfide), a TMDC (transition metal dichalcogenide) material with a two-dimensional crystal structure, has attracted attention.

Weaknesses of TMDC material MoS2:

MoS2 is

“High contact resistance at the contact surface with the metal electrode”

It was “a factor that suppresses the drive current and hinders performance improvement”.

How to eliminate high contact resistance:

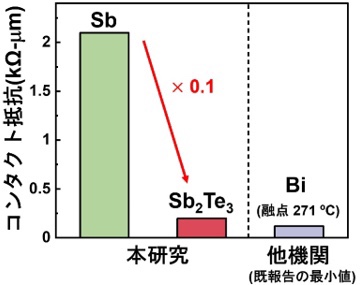

If “semimetals such as Bi (bismuth) and Sb (antimony)” are used as contact materials, it can be greatly reduced.

but,

Bi (bismuth) and Sb (antimony) had a problem of “low thermal stability due to low melting point”.

Research group:

We made full use of the “sputtering method suitable for mass production”.

The problem was solved by forming a film of Sb2Te3 (diantimony tritelluride) on a single layer of MoS2.

As a result, the contact resistance of the transistor is greatly reduced.

What is Sb2Te3:

It is known to have a high melting point of 620°C, while having properties similar to those of semimetals.

We achieved low contact resistance while maintaining high heat resistance.

Future CMOS fabrication:

We aim to fabricate CMOS by connecting n-type and p-type TMDC transistors in series.

We will continue to develop other contact materials suitable for p-type TMDCs.

-PC Watch

https://pc.watch.impress.co.jp/docs/news/1478116.html

AIST: Development of new structure transistor for 2nm generation

– Significant improvement in integration by stacked Si/Ge heterogeneous channel complementary field effect transistors –

point

Japan-Taiwan semiconductor R&D base: building Si/Ge heterogeneous channel integration platform for 2nm generation

Si n-type field effect transistor/Ge p-type field effect transistor: Achieving a new structure of vertically stacked transistors

A new step toward realizing large-scale integrated circuits capable of high-speed information processing with low power consumption

https://www.aist.go.jp/aist_j/press_release/pr2020/pr20201208/pr20201208.html

Transistor de nouvelle génération 2 nm : technologie développée à faible résistance de contact !

ーAIST : Réalisation de performances supérieures dans les semi-conducteurs logiques 2nmー

ーJapon-Taïwan : construire une plate-forme d’intégration de canaux hétérogènes Si/Ge 2nmー

AIST

Université métropolitaine de Tokyo

Le groupe de recherche a développé une “technologie à faible résistance de contact qui améliore les performances des transistors MoS de type n”.

Il peut contribuer à améliorer les performances des semi-conducteurs logiques de nouvelle génération.

Transistors de nouvelle génération au-delà de 2 nm :

En tant que matériau semi-conducteur pour le canal,

MoS2 (disulfure de molybdène), un matériau TMDC (dichalcogénure de métal de transition) avec une structure cristalline bidimensionnelle, a attiré l’attention.

Faiblesses du matériau TMDC MoS2 :

MoS2 est

“Haute résistance de contact à la surface de contact avec l’électrode métallique”

C’était “un facteur qui supprime le courant d’entraînement et entrave l’amélioration des performances”.

Comment éliminer la résistance de contact élevée :

Si “des semi-métaux tels que Bi (bismuth) et Sb (antimoine)” sont utilisés comme matériaux de contact, cela peut être considérablement réduit.

mais,

Bi (bismuth) et Sb (antimoine) avaient un problème de “faible stabilité thermique en raison d’un point de fusion bas”.

Groupe de recherche:

Nous avons pleinement utilisé la “méthode de pulvérisation adaptée à la production de masse”.

Le problème a été résolu en formant un film de Sb2Te3 (tritellurure de diantimoine) sur une seule couche de MoS2.

En conséquence, la résistance de contact du transistor est fortement réduite.

Qu’est-ce que Sb2Te3 :

Il est connu pour avoir un point de fusion élevé de 620°C, tout en ayant des propriétés similaires à celles des semi-métaux.

Nous avons obtenu une faible résistance de contact tout en maintenant une résistance élevée à la chaleur.

Fabrication du futur CMOS :

Notre objectif est de fabriquer du CMOS en connectant en série des transistors TMDC de type n et de type p.

Nous continuerons à développer d’autres matériaux de contact adaptés aux TMDC de type p.

-Montre PC

AIST : Développement d’une nouvelle structure de transistor pour la génération 2nm

– Amélioration significative de l’intégration par des transistors à effet de champ complémentaires à canaux hétérogènes Si/Ge empilés –

indiquer

Base de R&D Japon-Taiwan sur les semi-conducteurs : création d’une plate-forme d’intégration de canaux hétérogènes Si/Ge pour la génération 2 nm

Transistor à effet de champ de type Si n/transistor à effet de champ de type Ge p : réalisation d’une nouvelle structure de transistors empilés verticalement

Une nouvelle étape vers la réalisation de circuits intégrés à grande échelle capables de traiter l’information à grande vitesse avec une faible consommation d’énergie

2-nm-Transistor der nächsten Generation: Entwickelte Technologie mit niedrigem Kontaktwiderstand!

ーAIST: Realisierung einer höheren Leistung in 2-nm-Logikhalbleiternー

ーJapan-Taiwan: Aufbau einer heterogenen 2-nm-Si/Ge-Kanalintegrationsplattformー

AIST

Tokyo Metropolitan University

Die Forschungsgruppe hat eine „Technologie mit niedrigem Kontaktwiderstand entwickelt, die die Leistung von MoS-Transistoren vom n-Typ verbessert“.

Es kann dazu beitragen, die Leistung von Logikhalbleitern der nächsten Generation zu verbessern.

Transistoren der nächsten Generation jenseits von 2 nm:

Als Halbleitermaterial für den Kanal

MoS2 (Molybdändisulfid), ein TMDC-Material (Übergangsmetalldichalkogenid) mit einer zweidimensionalen Kristallstruktur, hat Aufmerksamkeit erregt.

Schwächen des TMDC-Materials MoS2:

MoS2 ist

„Hoher Übergangswiderstand an der Kontaktfläche zur Metallelektrode“

Es war “ein Faktor, der den Antriebsstrom unterdrückt und die Leistungsverbesserung behindert”.

So beseitigen Sie hohe Kontaktwiderstände:

Werden als Kontaktwerkstoffe „Halbmetalle wie Bi (Bismut) und Sb (Antimon)“ verwendet, lässt sie sich stark reduzieren.

Aber,

Bi (Bismut) und Sb (Antimon) hatten ein Problem der “geringen thermischen Stabilität aufgrund des niedrigen Schmelzpunkts”.

Forschungsgruppe:

Wir haben das „massentaugliche Sputterverfahren“ voll ausgeschöpft.

Das Problem wurde gelöst, indem ein Film aus Sb2Te3 (Diantimontritellurid) auf einer einzelnen Schicht aus MoS2 gebildet wurde.

Dadurch wird der Kontaktwiderstand des Transistors stark reduziert.

Was ist Sb2Te3:

Es ist bekannt, dass es einen hohen Schmelzpunkt von 620°C hat, während es ähnliche Eigenschaften wie Halbmetalle hat.

Wir erreichten einen niedrigen Kontaktwiderstand bei gleichzeitig hoher Hitzebeständigkeit.

Zukünftige CMOS-Fertigung:

Unser Ziel ist es, CMOS herzustellen, indem wir TMDC-Transistoren vom n-Typ und p-Typ in Reihe schalten.

Wir werden weiterhin andere Kontaktmaterialien entwickeln, die für TMDCs vom p-Typ geeignet sind.

-PC-Uhr

AIST: Entwicklung eines Transistors mit neuer Struktur für die 2-nm-Generation

– Signifikante Verbesserung der Integration durch gestapelte Si/Ge-Feldeffekttransistoren mit heterogenen Kanälen –

Punkt

Japan-Taiwan-Halbleiter-F&E-Basis: Aufbau einer heterogenen Si/Ge-Kanal-Integrationsplattform für die 2-nm-Generation

Si-n-Typ-Feldeffekttransistor/Ge-p-Typ-Feldeffekttransistor: Erreichen einer neuen Struktur von vertikal gestapelten Transistoren

Ein neuer Schritt zur Realisierung hochintegrierter Schaltkreise, die zur Hochgeschwindigkeits-Informationsverarbeitung bei geringem Stromverbrauch fähig sind

Sb2Te3/MoS2 Van der Waals Junctions with High Thermal Stability and Low Contact Resistance

– X-MOL

Two-dimensional transition metal

dichalcogenides (TMDCs)

demonstrate great potential in nanoelectronics devices owing to their high carrier mobility in the atomically thin channel regime.

However, high contact resistance between source/drain electrodes and TMDC channels

hinders the TMDCs applications in the very-large-scale integration (VLSI) field.

Here, this work reports

atomically aligned van der Waals (vdW) junction fabrications through thermal-induced crystallization of layered Sb2Te3electrodes on monolayer MoS2 using VLSI-compatible physical vapor deposition and annealing processes.

Due to Fermi-level unpinning with a small band offset between Sb2Te3 and MoS2 and small density of state of Sb2Te3,

better device performance is demonstrated on MoS2 MOSFETs with Sb2Te3/W contact than that of Sb/W contact.

Moreover,

the ideal vdW junctions are found to demonstrate extreme high-thermal robustness.

No intermixing at the Sb2Te3/MoS2 interface or crystallinity degradation of Sb2Te3 is observed

after 450 °C annealing, leading to higher thermal stability than its Sb counterpart.

Sb2Te3 is a promising candidate as an n-type contact material for TMDC-based devices such as MoS2, MoSe2, and WS2 in future VLSI electronics and various other applications.