The University of Tokyo: Developed 3D integrated memory: Solved the von Neumann bottleneck

-Simultaneous integration of high mobility transistor and ferroelectric capacitor-

2021.06.01

The University of Tokyo and Kobe Steel: [Press release]

◆ Achieves ferroelectric capacitors

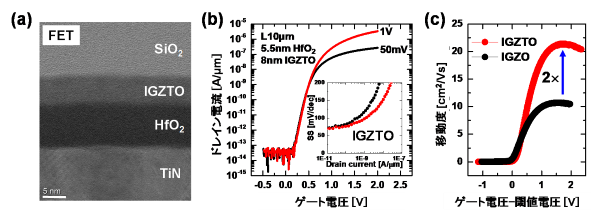

Using IGZO material with Sn added,

Transistors with mobility more than twice as high as before,

We have realized a ferroelectric capacitor that can be formed by a low temperature process of 400 ° C or less.

◆ Demonstration of operation of 3D integrated memory

High mobility transistor and

Simultaneously integrating ferroelectric capacitors

We have succeeded in demonstrating the operation of a memory device that can be integrated in three dimensions.

◆ Implement machine learning on edge devices

With this memory device technology

Machine learning can be implemented on edge devices,

The development of more advanced social services using artificial intelligence is expected.

Associate Professor Kobayashi, University of Tokyo,

Kobe Steel,

Kobelco Research Institute,

Developed 3D integrated memory device:

A transistor using IGZO with Sn added and a ferroelectric HfO2 capacitor are integrated.

We have succeeded in developing a memory device technology that can be embedded in the wiring layer of an integrated circuit of a processor.

Traditional machine learning algorithms:

Machine learning algorithms require efficient data transmission between large memory and processors.

However, the main memory is currently implemented on a separate chip from the processor.

Data transmission efficiency between chips is poor, and machine learning calculation processing is delayed.

This is called the von Neumann bottleneck.

Resolve the von Neumann bottleneck:

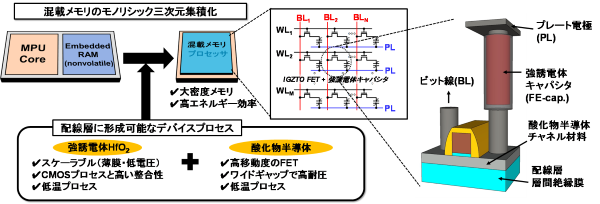

In order to achieve both large-capacity memory and highly efficient data transmission, a mixed memory device that can be three-dimensionally integrated directly into the wiring layer of the integrated circuit of the processor is an effective solution.

Large capacity memory on the processor wiring layer:

We have realized a large-capacity memory that can be integrated three-dimensionally on the wiring layer of the processor.

Can be wired directly above the processor

Improved data transmission efficiency,

High energy efficient execution of machine learning,

The above two points are now possible.

Achievements this time:

Machine learning can be calculated with high energy efficiency.

Improved performance of edge devices

By performing advanced artificial intelligence calculations on edge devices, it is expected that big data services will be dramatically improved.

Institute of Industrial Science, University of Tokyo

https://www.iis.u-tokyo.ac.jp/ja/news/3569/

Closer hardware systems bring the future of artificial intelligence into view

Machine learning is the process by which computers adapt their responses without human intervention.

This form of artificial intelligence (AI)

is now common in everyday tools such as virtual assistants and is being developed for use in areas from medicine to agriculture.

A challenge posed by the rapid expansion of machine learning is the high energy demand of the complex computing processes.

Researchers from The University of Tokyo

have reported the first integration of a mobility-enhanced field-effect transistor (FET) and a ferroelectric capacitor (FE-CAP)

to bring the memory system into the proximity of a microprocessor and improve the efficiency of the data-intensive computing system.

Their findings were presented at the 2021 Symposium on VLSI Technology.

Memory cells require both a memory component and an access transistor.

In currently available examples, the access transistors are generally silicon-metal-oxide semiconductor FETs.

While the memory elements can be formed in the ‘back end of line’ (BEOL) layers,

the access transistors need to be formed in what are known as the ‘front end of line’ layers of the integrated circuit, which isn’t a good use of this space.

In contrast, oxide semiconductors such as indium gallium zinc oxide (IGZO)

can be included in BEOL layers because they can be processed at low temperatures.

By incorporating both the access transistor and the memory into a single monolith in the BEOL,

high-density, energy-efficient embedded memory can be achieved directly on a microprocessor.

The researchers

used IGZO doped with tin (IGZTO) for both the oxide semiconductor FET and ferroelectric capacitor (FE-cap) to create 3D embedded memory.

“The proximity achieved with our design will significantly reduce the distance that signals must travel, which will speed up learning and inference processes in AI computing, making them more energy efficient,”

study author Masaharu Kobayashi explains.

– Institute of Industrial Science, the University of Tokyo