TSMC 3DFabric: Established alliance with 19 companies!

– Japan’s IBIDEN and Advantest Participate –

Taiwan TSMC:

Using TSMC’s mounting technology “3DFabric”,

To support the development of semiconductors,

Launched OIP (Open Innovation Platform) 3DFabric Alliance.

Announced on October 27, 2022.

3D Fabric Alliance:

Combine multiple chiplets into a single package.

Recently, there has been an increasing interest in heterogeneous integration semiconductors.

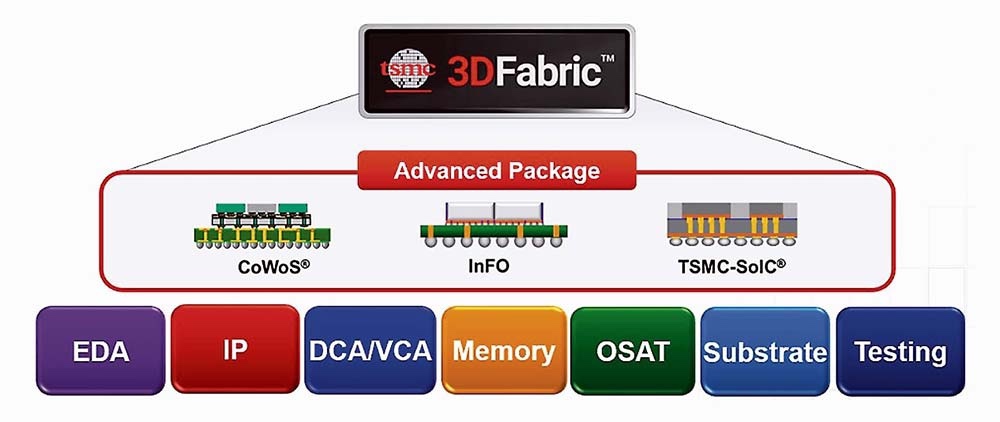

3D Fabric is:

CoWoS (Chip on Wafer on Substrate)

InFO (Integrated Fan-Out)

“TSMC-SoIC”

It consists of three semiconductor technologies.

These can be used in combination (Fig. 1)

“CoWoS and InFO” refers to 2.5D packaging technology.

“TSMC-SoIC” mainly refers to 3D packaging technology.

note that,

Package on Package: Place a package on top of another package.

PoP (Package on Package): One type of InFO (InFO_PoP)

TSMC-SoIC: More advanced than general 3D packaging technology (Fig. 2)

Chip on Wafer:

TSMC-SoIC has SoIC-CoW (Chip on Wafer) that stacks dies on a wafer,

Wafer on Wafer:

There is SoIC-WoW (Wafer on Wafer) in which wafers are stacked and then diced.

Nikkei Cross Tech (xTECH)

https://xtech.nikkei.com/atcl/nxt/column/18/01537/00546/

TSMC 3DFabric : alliance établie avec 19 entreprises !

– Les japonais IBIDEN et Advantest participent –

Taïwan TSMC :

En utilisant la technologie de montage “3DFabric” de TSMC,

Pour accompagner le développement des semi-conducteurs,

Lancement de l’OIP (Open Innovation Platform) 3DFabric Alliance.

Annoncé le 27 octobre 2022.

Alliance Tissu 3D :

Combinez plusieurs chiplets dans un seul paquet.

Récemment, il y a eu un intérêt croissant pour les semi-conducteurs à intégration hétérogène.

Le tissu 3D est :

CoWoS (puce sur plaquette sur substrat)

InFO (sortance intégrée)

“TSMC-SoIC”

Il se compose de trois technologies de semi-conducteurs.

Ceux-ci peuvent être utilisés en combinaison (Fig. 1)

“CoWoS et InFO” fait référence à la technologie d’emballage 2.5D.

“TSMC-SoIC” fait principalement référence à la technologie d’emballage 3D.

Notez que,

Colis sur colis : Placez un colis au-dessus d’un autre colis.

PoP (Package on Package) : Un type d’InFO (InFO_PoP)

TSMC-SoIC : plus avancé que la technologie d’emballage 3D générale (Fig. 2)

Puce sur plaquette :

TSMC-SoIC a SoIC-CoW (Chip on Wafer) qui empile les matrices sur une plaquette,

Plaquette sur plaquette :

Il existe le SoIC-WoW (Wafer on Wafer) dans lequel les wafers sont empilés puis découpés en dés.

Nikkei CrossTech (xTECH)

TSMC 3DFabric: Gegründete Allianz mit 19 Unternehmen!

– Japans IBIDEN und Advantest nehmen teil –

Taiwan-TSMC:

Mit der Befestigungstechnologie “3DFabric” von TSMC,

Um die Entwicklung von Halbleitern zu unterstützen,

Einführung der OIP (Open Innovation Platform) 3DFabric Alliance.

Angekündigt am 27. Oktober 2022.

3D-Fabric-Allianz:

Kombinieren Sie mehrere Chiplets in einem einzigen Paket.

In letzter Zeit besteht ein zunehmendes Interesse an Halbleitern mit heterogener Integration.

3D-Gewebe ist:

CoWoS (Chip auf Wafer auf Substrat)

InFO (Integrierter Fan-Out)

“TSMC-SoIC”

Es besteht aus drei Halbleitertechnologien.

Diese können in Kombination verwendet werden (Abb. 1)

“CoWoS und InFO” bezieht sich auf die 2,5-D-Verpackungstechnologie.

“TSMC-SoIC” bezieht sich hauptsächlich auf 3D-Packaging-Technologie.

beachten Sie, dass,

Paket auf Paket: Legen Sie ein Paket auf ein anderes Paket.

PoP (Package on Package): Eine Art von InFO (InFO_PoP)

TSMC-SoIC: Fortschrittlicher als die allgemeine 3D-Packaging-Technologie (Abb. 2)

Chip auf Wafer:

TSMC-SoIC hat SoIC-CoW (Chip on Wafer), das Chips auf einem Wafer stapelt,

Waffel auf Waffel:

Es gibt SoIC-WoW (Wafer on Wafer), bei dem Wafer gestapelt und dann gewürfelt werden.

Nikkei Cross Tech (xTECH)

TSMC Launches OIP 3DFabric Alliance to Shape the Future of Semiconductor and System Innovations

– Semiconductor Digest

OIP 3DFabric Alliance

As the industry’s most comprehensive and vibrant ecosystem,

the TSMC OIP consists of six alliances:

the EDA Alliance,

IP Alliance,

Design Center Alliance (DCA),

Value Chain Alliance (VCA),

Cloud Alliance,

and now, the 3DFabric Alliance.

TSMC launched OIP in 2008

to help customers overcome the rising challenges of semiconductor design complexity by creating a new paradigm of collaboration,

organizing development and optimization

across TSMC’s technologies, electronic design automation (EDA), IP, and design methodology.

Partners of the new 3DFabric Alliance

have early access to TSMC’s 3DFabric technologies,

enabling them to develop and optimize their solutions in parallel with TSMC.